- 博客(24)

- 资源 (1)

- 收藏

- 关注

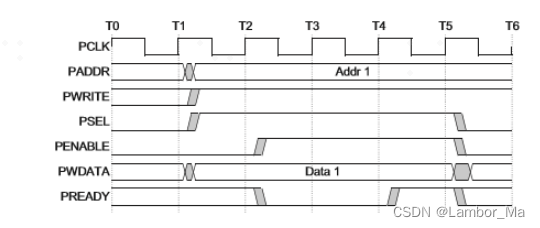

原创 AMBA-APB 协议介绍

系列文章目录文章目录系列文章目录前言一、APB二、APB signals三、write transfersno wait stateswait states四、Read transfersno wait states 1284

1284

原创 verilog中简单的one-hot 状态机转换

简单的one-hot 状态机转换one-hot 编码verilog中写法one-hot 编码0001 0010 0100 1000如上例每次只有1个bit位置high其余low的状态叫one-hot,相反只有1个bit low 其余bit high 叫 one-cold。verilog中写法一般状态机转换中我们会先paremeter A = 0001, B = 0010, C = 0100, D = 1000;像这样预设值,这里介绍一种新的方法,如上图的变化,如果state想变到 A状态

2021-01-04 07:41:15

2895

2895

原创 verilog中边沿检测器,双边沿检测器和双边沿触发寄存器的理解和写法

verilog中边沿检测器,双边沿检测器和双边沿触发寄存器的理解和写法单边沿检测电路图双边沿检测电路图下降沿检测保持器件电路图双边沿触发寄存器(DDR)单边沿检测电路图根据电路图很好理解, 为了让原来的信号保持一下也可以说是延迟一个时钟,就能做出上升沿的判断,后面加入一个寄存器的目的就是为了让检测延迟一个时钟显示,也保证检测只持续一个时钟。module top_module ( input clk, input [7:0] in, output [7:0] pedge);

2021-01-03 09:50:40

2951

2951

原创 数字电路中卡诺图理解

简单理解就是,卡诺图是用来化简数字逻辑的图表,它将不同输入变量的组合枚举到图表中,然后填入是否为1或者0. 化简有2种方式1种是SOP一种是POS。SOPsum of products就是 P = ab+ bc + abc 这种形式化简方法为:1.圈出相邻的1(4个角也可以认为是相邻的)2.化简写出每个圈的最简式子3.将最简式相加举例假设A圈是 BD构成,B圈是B’ D’构成,则最后结果是 BD+B’D’POSproduct of sum就是P =(a+b)(c+d) 这种形式化简

2021-01-03 08:51:19

3134

3134

1

1

原创 verilog中全加器行为级别(+ verilog中会自动添加进位)

module top_module ( input [3:0] x, input [3:0] y, output [4:0] sum); // This circuit is a 4-bit ripple-carry adder with carry-out. assign sum = x+y; // Verilog addition automatically produces the carry-out bit. // Verilog quirk: Even though the va

2020-12-26 04:43:33

500

500

1

1

原创 verilog中 在选择vector部分的时候无法使用variable变量的问题

经常碰到的问题就是使用一个vector的时候input [11:0] a;想每隔4个取一组 即a[3:0] a[7:4] a[11:8]for(genvar i =0; i<3 : i = i+1)a[(i*4+3):i*4]这种形式会报错 i is not constant file. 这种错误,表示verilog不知道这个a选取的时候是不是一个固定值。解决方法有两种一用连接符a={in[i*4+3],in[i*4+2],in[i*4+1],in[i*4+0]}每个相应位置选取

2020-12-25 00:06:52

785

785

原创 verilog中 case写法避免写default的巧妙写法

always @(*) begin out = '1; // '1 is a special literal syntax for a number with all bits set to 1. // '0, 'x, and 'z are also valid. // I prefer to assign a default value to 'out' instead of using a // default case. case (sel) 4'h0: out

2020-12-24 23:19:59

2787

2787

4

4

原创 casez优先编码

always @(*) begincasez (in[3:0])4’bzzz1: out = 0; // in[3:1] can be anything4’bzz1z: out = 1;4’bz1zz: out = 2;4’b1zzz: out = 3;default: out = 0;endcaseendz位置case不管是什么都可。

2020-12-24 23:18:15

179

179

原创 verilog中 blocking assignment 和non-blocking assignment的区别(阻塞赋值和非阻塞赋值的区别)

阻塞赋值与非阻塞赋值:1.阻塞赋值“=”(组合逻辑电路),非阻塞赋值“<=”(时序逻辑电路);2.Verilog模块编程的8个原则:(1) 时序电路建模时,用非阻塞赋值。(2) 锁存器电路建模时,用非阻塞赋值。(3) 用always块建立组合逻辑模型时,用阻塞赋值。(4) 在同一个always块中建立时序和组合逻辑电路时,用非阻塞赋值。(5) 在同一个always块中不要既用非阻塞赋值又用阻塞赋值。(6) 不要在一个以上的always块中为同一个变量赋值。(7) 用$s

2020-12-22 21:51:14

1402

1402

原创 VHDL中 inout vs buffer out 的区别

inout - is used for ports that can both be an output and an input. They’re called tri state buffersif you define a port as inout, you also have to define it’s behaviour.Suppose "some_inout " is defined as an inout std_logic port in your entity.Code:som

2020-11-01 22:02:02

1026

1026

原创 数字IC必修之Verilog知识点——Task和Function,System Task(系统函数), System Function, Verilog-2001

task和functiontask 和 function 的声明在module内部,且不需要先于调用之前。task:只能在procedural 内部调用,task的调用方式是statement本身,而不是表达式。function:可以在module的任何地方调用,是作为一种operands来使用。tasktask可以有0个或多个argument(即input output), 可以有延时,上升沿下降沿的使用。使用时的典型例子: read_reg(input [31:0] add, ..

2020-08-06 04:15:47

1012

1012

原创 数字IC必修之Verilog知识点——时序逻辑(sequential logic),锁存器,异步&同步触发器flipflops,N位移位寄存器,计数器,FSM三段式状态机

Flip-Flopsasynchronous (异步中CDC)synchronous(同步时钟)时钟上升沿到来后,会产生的FSMs:有限状态机在同步时钟中一般用状态机来进行控制——structural view(FFs separate from combinational logic)——behavioral view(synthesis of sequencers)Latch with Reset第二个if没有else连接,所以当g=0时,Q锁存原来的值。异步复位F..

2020-08-05 22:56:53

766

766

原创 数字IC必修之Verilog知识点——系统任务,综合器指令,parameter重要性,testbench规范(面试小白考试)

System Tasks$display("…",arg2,arg3,…); 打印数据$monitor("…",arg2,arg3,…); 数据变化时才打印$stop suspends sim when encountered$finish finishes sim when encountered$fopen(“filename”); 返回file descriptor(integer); then, use $fdisplay(fd,"…",arg2,arg3,…); or #fmoni.

2020-08-05 03:58:49

289

289

原创 数字IC必修之Verilog知识点——模块建立及常用语法总结过程块中的语法(面试小白考试)

Modulemodule my_module(out1,…,inN) ;output out1,…,outM;input in1,…,inN;…// declarations…// description of f (maybe sequential)endmoduleContinuous Assignmentsassign #de1 (net type) = expr;inside a moduleoutside procedures(always可综合 initial不..

2020-08-04 23:42:02

461

461

原创 数字IC必修之Verilog知识点入门——基础知识基本变量及操作符(面试小白考试)

命名开头不能使用数字和标识符分大小写行注释//块注释/*xxxxx*/value : 0,1,x(悬空态,unknown logic),z(高阻态)Verilog中数字表达形式 12‘0 3zx7 = 011zzzxxx111Bit extension: 0,x or z 可以extend 。 其他extend前面加0Net: 逻辑驱动的硬件导线,不连接时是‘z’态,有四种线分别是 wire, wand,wor,tri线与,线或逻辑一般不用因为会造成一条线被2种驱动wire Y = A&.

2020-08-04 18:42:56

934

934

原创 工程师需要掌握的Linux系统操作指令和Vim常用操作指令

Linux 系统操作cd … 返回上一级 (… 父目录, . 自身目录)mkdir tmp 创建目录touch xxx.txt 创建文件rmdir tmp 删除空目录rmdir -p xxx (-p删除子目录如果父目录也为空也删除父目录)rm xxx.txt 删除文件 也可删除目录rm -rf 删除目录(-f 不询问是否删除)ln -s ll.log ll.rpt 为 ll.log 创建软链接ll.log 类似于window中的快捷方式ln ll.log ll.rpt

2020-07-25 17:55:00

197

197

原创 华为芯片ic数字岗笔试题(回忆版)

40道单选5道多选1.综合可综合语句判断2.Pll 3分频 是不是异步3.判断:综合面积大则PR面积大?4.-3.25 补码形式5.上升沿下降沿检测电路6.异步fifo 空满信号产生判断7.测试点 覆盖率8.竞争冒险9.STA缺点10.影响静态功耗问题11.异步同步电路信号判断 什么是同步时钟12.常见主流测试平台13.STA相关问题 比如一般检测的时序分析路径是什么14.一大推关于测试的不好意思只记得个大概,自我感觉都是一些常规笔试题目。...

2020-07-15 20:47:00

6500

6500

3

3

原创 看youtube做笔记之Python 脚本入门(Modules AWS and GUI)

Python ScriptingIntroductionModules In Python ScriptingSys ModuleOs moduleSubprocess ModuleMath ModuleRandom ModuleDate Time ModuleJson ModuleAWS scriptingGUI programingIntroductionModules In Python ScriptingSys ModuleOs module对文件进行操作: 移动、创建、删除impo

2020-05-31 19:14:23

305

305

转载 Big O notation explaination (算法效率和大O符号)

A beginner’s guide to Big O notationBig O notation is used in Computer Science to describe the performance or complexity of an algorithm. Big O specifically describes the worst-case scenario, and can be used to describe the execution time required or the

2020-05-29 20:55:57

342

342

原创 二极管电路表示数字逻辑电路 --面试题

二极管表示与或逻辑二极管特性与门电路由二极管实现或门电路由二极管实现二极管特性正向导通时一般二极管上的电压维持不变,(锗管约为 0.3V,硅管约为 0.7V),称为正向压降,如果电压过大可以近似为没有电压。反向导通时,二极管几乎没有电流通过,处于截止状态。与门电路由二极管实现解析:当A、B中有一个的电压为低电压时,Y处电压为0.7V(正向导通电压)。因为Vcc提供的压降可以满足其中一个二极管正向导通。所以只有当A、B均是高电压时,Y处电压才能为A、B提供的高电压+0.7V(3V+0.7V)。

2020-05-27 20:57:36

933

933

原创 补码运算加减原则--面试题

这里写目录标题补码概念补码加减法补码概念正数补码是其本身:e.g. 0001 -> 0001负数补码:保留符号位,取反加一。e.g. 1001-> 1111补码加减法加法:1.正数与负数00011110 (补)+ 10011100(补)= 10111010(补)10111010(补) 保留符号位转换成原码 11000110(原)30+(-100)= -702.正数与正数0001+0001=00103.负数与负数1010(原)+1010(原)= 0100 (原) 保留

2020-05-27 20:12:34

398

398

原创 波特图,极点和零点分析与公式

波特图理解和极零点公式极零点概念极点零点极零点概念零点:当系统输入幅度不为零且输入频率使系统输出为零时,此输入频率值即为零点。极点:当系统输入幅度不为零且输入频率使系统输出为无穷大(系统稳定破坏,发生振荡)时,此频率值即为极点。每一个极点之处,增益衰减-3db,并移相-45度。极点之后每十倍频,增益下降20db.零点与极点相反;每一个零点之处,增益增加3db,并移相45度。零点之后,每十倍频,增益增加20db。极点公式:Pole Location = fP (cutoff freq)M

2020-05-27 19:05:42

15182

15182

原创 verilog中一文搞懂有限状态机(FSM)Mealy和Moore状态机(及一段式,二段式,三段式)

testbenchverilog示例verilog示例module adder(clk,rst,q_out,k)input clk,rst,k;out q_out;localparam S1 = 0, S2=1, S3=2;reg[1:0] state, nextstate;always @(posedge clk or posedge rst) begin if

2020-05-27 12:30:42

6001

6001

原创 Perl基本及常用习题教程

Perl 基本语句和习题基本数据类型关联数组(hash数组)正则表达式习题基本数据类型perl 中注释为##!/usr/bin/perl //脚本开头声明$a=123;$b="Hello world";@x = (1,2,3,5); //数组$c=@x;$d=$#x;print "$a\n";print "$b\n";print "$c\n"; //代码中数量个数print"$d\n"; //最后一个数的下角标,此例中有0~3个数,即输出因为3pirnt"$x[3]\n"

2020-05-26 23:38:27

846

846

空空如也

TA创建的收藏夹 TA关注的收藏夹

TA关注的人

RSS订阅

RSS订阅